在先进半导体封装领域,混合键合(Hybrid Bonding)作为一项突破性技术,正逐步成为推动芯片集成度提升和性能优化的关键手段。该技术通过直接实现芯片间金属与介电层的键合,取代传统焊料连接,为高性能计算、人工智能和存储芯片等应用提供了高密度、低功耗的互连方案。

基本概念与工艺原理

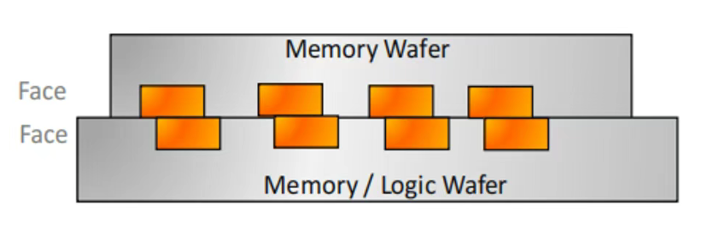

混合键合是一种用于芯片间(die-to-die)连接的先进封装技术,包括晶圆对晶圆(wafer-to-wafer)键合和芯片对晶圆(die-to-wafer)键合两种形式。其核心在于通过金属焊盘与周围氧化物的直接接触实现连接,无需任何填充材料如焊料。键合结构由氧化物键合与金属键合共同构成:金属焊盘会略微凹陷,使氧化物先发生键合,随后金属焊盘再完成键合。这种设计去除了焊料,提升了连接质量与电气性能,同时键合后的氧化物提供机械强度。

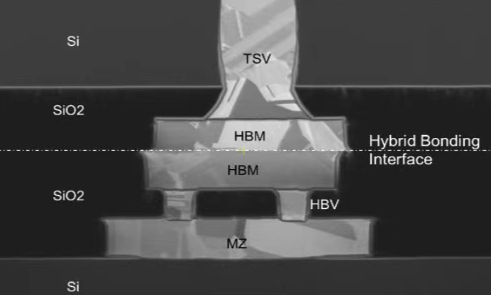

工艺原理方面,混合键合结合了介电键合和金属互连。基本流程始于表面预处理:晶圆需经过化学机械抛光/平坦化(CMP)和表面活化及清洗处理,以确保表面平整洁净且具亲水性。电介质的表面粗糙度阈值需低于0.5nm,铜焊盘则需低于1nm。

随后进行预对准键合:在室温下紧密贴合后,介质SiO₂上的悬挂键实现桥连,形成SiO₂-SiO₂间的键合。此步骤可能涉及热压键合或阳极键合,在温度(200-400°C)和压力(几十到几百牛顿)下促使介电材料分子形成化学键。

初始键合后,通过热退火处理(温度通常在300°C至400°C之间)促进介质SiO₂反应和金属Cu的互扩散,形成永久键合。退火过程中,铜因热膨胀系数大于SiO₂而体积膨胀,使两片晶圆上的铜相互接触并扩散,实现铜与铜之间的直接连接。

混合键合的类型与关键设备

混合键合主要分为晶圆到晶圆(Wafer-to-Wafer,W2W)键合和芯片到晶圆(Die-to-Wafer,D2W)键合两种类型。

W2W键合适用于面积较小、良率较高的芯片,如CMOS图像传感器和3D NAND,其优势在于对准和键合步骤分开,颗粒更少,更加干净,但无法执行晶圆分类来选择已知良好芯片,可能导致缺陷芯片粘合到良好芯片上。D2W键合适用于大芯片和异构集成,能够测试和键合已知良好芯片,提高良率,但更容易形成污染,且技术实现难度更高,主要体现在亚微米级对准精度和界面共面性控制。

关键设备包括晶圆键合设备、芯片键合设备和表面处理设备。设备核心组件包括高精度对准系统、真空系统、温度控制系统、压力控制系统、清洁模块和等离子体激活模块。

应用案例与技术优势

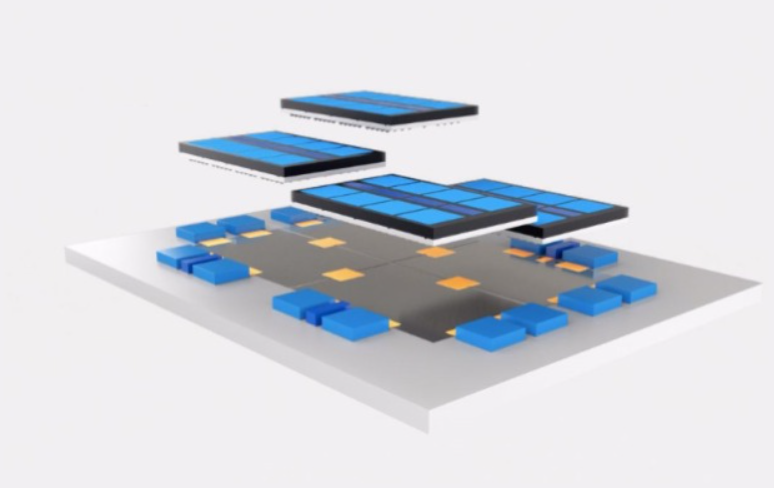

混合键合已在多个领域实现应用。在3D芯片堆叠中,AMD的3D V-Cache技术采用台积电SoIC-X的die-to-wafer混合键合,将CPU与额外缓存芯片紧密连接,提升系统性能;HBM高带宽内存通过混合键合实现多层堆叠,增加带宽。在异构集成方面,该技术使不同工艺节点制造的芯片(如射频芯片、传感器、处理器)有效结合,形成高性能封装体,应用于物联网设备和智能手机。图像传感器领域,混合键合将像素阵列芯片与逻辑芯片分离,扩大背照式结构可用面积,如索尼CMOS图像传感器。此外,3D NAND存储、汽车电子与5G通信也逐步采用混合键合,以满足高集成、低延迟需求。

混合键合技术优势显著。首先,混合键合实现极高密度互连,互连间距可达亚微米级乃至纳米级,较热压键合技术提高15倍密度,允许更多连接点,增加数据通信带宽。其次,由于省去中间介质如焊锡,直接铜对铜连接具有更低电阻,降低信号传输能量损失和时间延迟,速度提升11.9倍,带宽密度提升191倍。第三,紧凑结构和直接导电路径改善热管理,降低20%堆叠热阻,提升散热效率。第四,推动2.5D和3D封装发展,减少87%的TSV互连面积需求,提升空间利用率,实现小型化与高性能封装。最后,功耗显著降低,耗能只有微凸块的三分之一甚至更低,混合键合芯片能耗降低20倍,HBM芯片降低17%动态功耗。

技术难点与挑战

【尽管优势突出,混合键合实施面临诸多挑战。工艺要求极为严格:清洁度需1级/ISO 3级或更好洁净室和设备,台积电和英特尔正迈向ISO 2或ISO 1级别;表面光滑度要求电介质粗糙度低于0.5nm,铜焊盘低于1nm;对准精度需达到±100nm甚至更高。良率控制是另一大难点,颗粒是主要敌人,高度仅1微米的颗粒可导致直径10毫米的粘合空隙,从而引发键合缺陷,确保数十亿连接点成功键合难度大。热预算管理也需关注,例如HBM应用要求较低沉积和退火温度(低于300-350°C范围),以防止DRAM刷新退化。

成本问题突出,清洁度要求和工具增加导致成本大幅上升,混合键合工艺涉及许多传统上仅由晶圆厂专用的工具,OSAT公司经验较少,相关设备和材料成本较高。材料兼容性方面,需确保键合过程中不同材料间热膨胀系数匹配,否则可能导致应力问题和可靠性挑战。工艺集成挑战包括流程复杂、产业链配套能力不足,以及增加未使用技术。

此外,在3D集成中,良率问题更为凸显,如果任何芯片失效,整个堆叠结构都会受影响,需通过已知合格芯片(KGD)方案解决,但D2W键合可能引入切割碎屑污染,需采用激光切割和等离子切割等先进技术缓解。热管理也构成挑战,堆叠层数越多,散热越困难,可能限制3D集成优势。

本文转载自:Jeff的芯片世界

转载内容仅代表作者观点

不代表上海隐冠半导体立场